LIVE WEBINAR: Creating an AXI4 Lite, Transaction Based VHDL Testbench with OSVVM

Presenter: Jim Lewis, VHDL User, Designer, Verification Engineer, Trainer, OSVVM developer, and IEEE VHDL Chair

Thursday, February 20, 2020

11:00 AM – 12:00 PM PST

|

Abstract:

Open Source VHDL Verification Methodology (OSVVM) simplifies your FPGA and ASIC verification tasks by providing utility and model libraries. Using these free, open source libraries you can create a simple, powerful, concise, and readable testbench that is suitable for either a simple FPGA block or a complex ASIC.

This webinar is a guided walk-through of the OSVVM verification framework and transactions provided by OSVVM models.

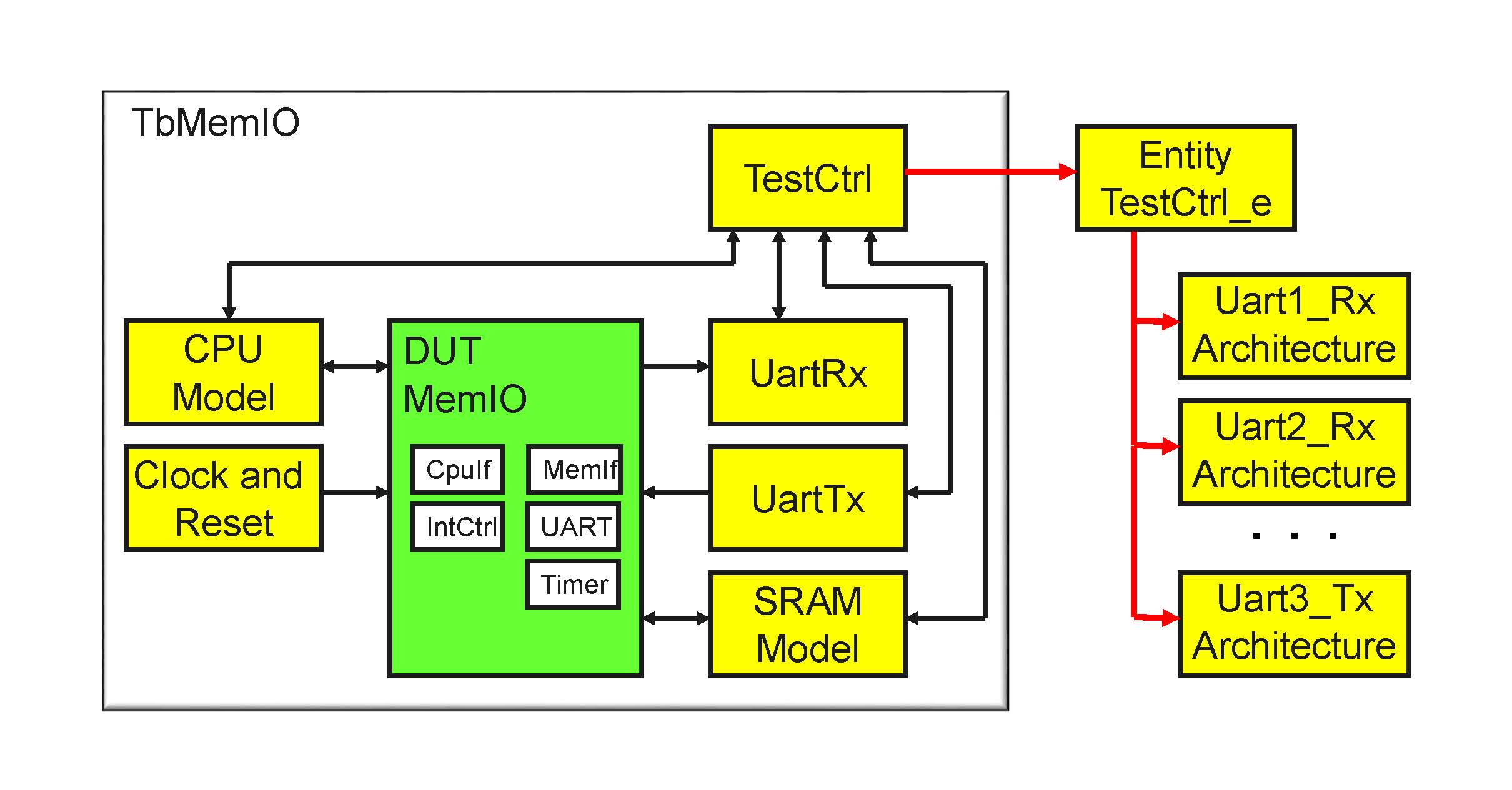

OSVVM's transaction based testbench approach is the current evolution of the approach taught by SynthWorks' for 20+ years. Looking at its block diagram, you will notice that its architecture looks similar to SystemVerilog + UVM.

Just like SystemVerilog, the OSVVM approach has a test sequencer, here named TestCtrl; it has transaction based models: Axi4Master, UartTx, and UartRx; and it has a test harness, named TbMemIO, which connects the test sequencer, verification models, and the DUT.

Just for clarity, in the OSVVM community, the word "model" generally refers to an entity and its corresponding architecture(s).

The test sequencer is a model that implements the test suite. Generally, there is one architecture for each different test in the test suite. Tests are written by calling procedures that implement transactions (interface operations such as MasterWrite, MasterRead, … or model directives such as WaitForClock). Hence an OSVVM test is looks something like the following:

log("Write and Read with ByteAddr = 0, 4 Bytes") ;

MasterWrite(AxiMasterTransRec, X"AAAA_AAA0", X"5555_5555" ) ;

MasterRead(AxiMasterTransRec, X"1111_1110", Data) ;

AffirmIfEqual(Data, X"2222_2222", "Master Read Data: ") ;

In OSVVM's transaction based methodology, randomization is separate from transaction dispatch (above calls to MasterWrite, MasterRead, …). Doing this simplifies the mixing of directed, algorithmic, file based, constrained random, and OSVVM's Intelligent Coverage Randomization tests.

The transaction based models, such as Axi4LiteMaster, receive transaction information from TestCtrl (such as Write value 5555_5555 to Address AAAA_AAA0) and convert it to appropriate waveforms on the DUT interface. The coding of these models can be either behavioral or RTL-like. Generally this means that the models written by the testbench team are easily read by the RTL design team. It also means the RTL team can write testbench models.

The test harness simply connects TestCtrl, the transaction based models (Axi4LiteMaster, …), and the DUT. This means it is just structural code – the same sort of code RTL code uses for connectivity.

Each transaction based model connects to TestCtrl using an OSVVM interface. An OSVVM interface is a record (one per model) that transfers transaction information. Currently an OSVVM interface is an inout of both models. As a result, the elements of the record use the resolution function resolved_max from the OSVVM package ResolutionPkg. However, when VHDL-2019 is adopted, we will be switching to the new VHDL Interfaces – which will replace the resolved record elements with a VHDL-2019 record view declaration.

Just like SystemVerilog + UVM, OSVVM offers a complete VHDL verification methodology from transaction based testbenches, to functional coverage and randomized test generation, to scoreboards and memory modeling, to error reporting and messaging, and to basic utilities (process synchronization).

Unlike SystemVerilog, OSVVM does not require a verification specialist. While we believe in independent verification – we also believe that an engineer should be able to be on the verification team on one project and the design team on the next.

Benefits of OSVVM

- Tests are Readable and Reviewable by All (Hardware, Verification, Software, and System Engineers)

- RTL designers can write Tests and/or Models

- Reuse and/or upgrade your current VHDL testbench and models

- OSVVM is modular – use the pieces you need now.

- Supports mixed test approaches (directed, algorithmic, file, constrained random, …)

- Same simple approach used for either small FPGAs or complex ASICs

Agenda:

- 50 min presentation/live demo

- 10 min Q&A

Presenter Bio:

Jim Lewis, the founder of SynthWorks, has twenty-eight years of design, teaching, and problem solving experience. In addition to working as a Principal Trainer for SynthWorks, Mr. Lewis does ASIC and FPGA design, custom model development, and consulting. Mr Lewis is a founding member of the Open Source VHDL Verification Methodology (OSVVM) and the principal architect of its packages and methodology. Mr. Lewis, who holds a BSEE, BSCEE, and MSEE from Purdue University, serves as chair of the IEEE 1076 VHDL Analysis and Standardization Working Group (VASG).

|