LIVE WEBINAR: UVVM steps up a gear: A review of some of the new features in this standardized VHDL verification methodology (EU)

Presenter: Espen Tallaksen, Founder of Bitvis

Thursday, April 2, 2020

3:00 PM – 4:00 PM CET

|

Abstract:

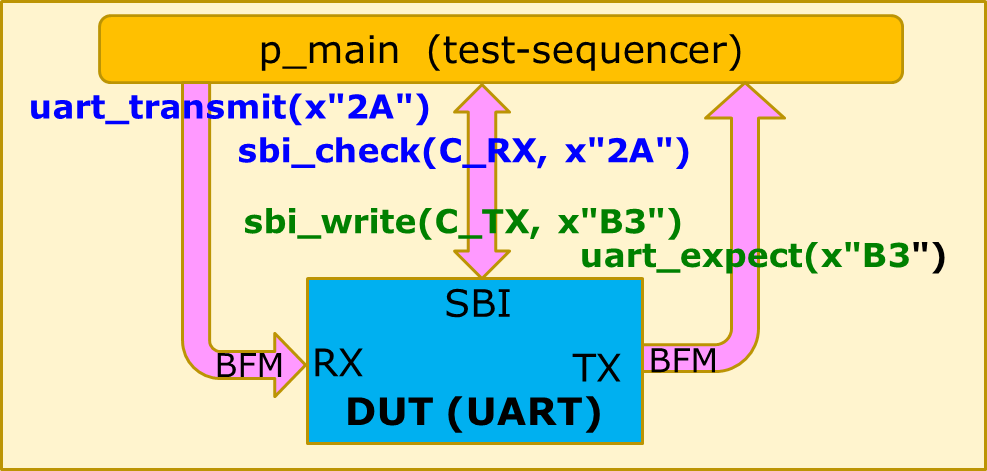

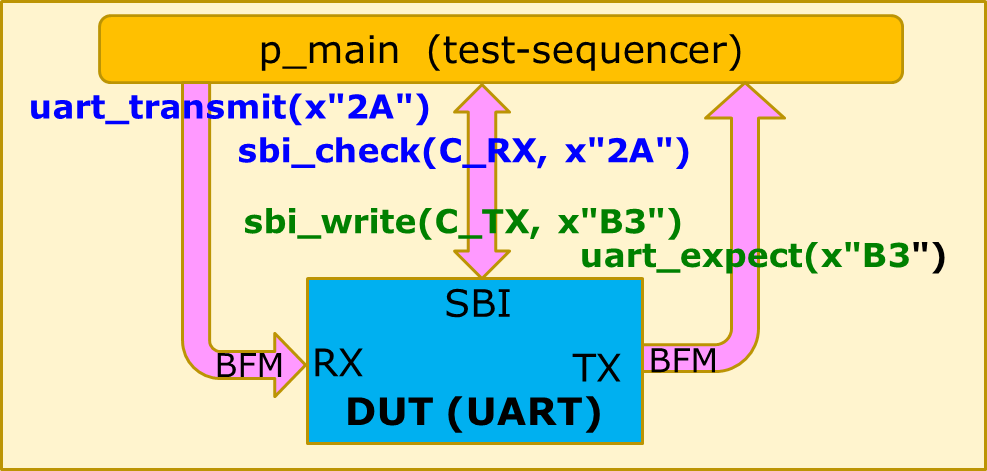

The verification of large or complex designs targeted at FPGAs is time consuming. However, with a good testbench architecture the workload can be greatly reduced. UVVM provides an ideal VHDL testbench architecture as well as a good reuse structure. Entry-level UVVM is easy, even for beginners. For more advanced verification, the standardized verification components, the high-level software-like commands and other features will allow complex verification scenarios to be handled in a structured and understandable way. UVVM is open source and provides a ‘kick-start’ testbench with BFMs and verification components for UART, SPI, AXI-lite, AXI stream, Avalon MM, Avalon stream, I2C, GPIO, SBI, GMII and Ethernet.

UVVM has been significantly updated through the ESA’s (European Space Agency’s) UVVM extension project. We have previously released the Scoreboard, and now lots of other new functionality has also been added.

The most important of these new functions are Activity Watchdog, Error Injection, Monitor, Hierarchical VVCs and Specification Coverage.

This presentation will provide an introduction to UVVM Utility Library, BFMs and VVCs, and then go through the new features and explain how they will help you make a better testbench and, in doing so, shorten your overall project development times.

The usage of UVVM is exploding, and all the new features are already greatly appreciated by the VHDL community.

UVVM is the best possible solution for all the features needed for the most efficient FPGA development and high-quality products:

- The best possible Overview, Readability, Maintainability

- The simplest possible control of large or complex testbenches

- Unique Reusability

Agenda:

- Brief intro to TB infrastructure

- Simple data communication

- High level transactions and Verification Components

- All the new functionality

- Specification Coverage in more detail

- Summary

- Live demo

- Conclusion

- Q&A

Presenter Bio:

Espen Tallaksen, Founder and CTO of Bitvis.

Espen Tallaksen graduated from the University of Glasgow (Scotland) in 1987 and has 30 years’ experience with FPGA and ASIC development from Philips Semiconductors in Switzerland and various companies in Norway, including his earlier founded company Digitas. For twenty years Espen has had a special interest for methodology cultivation and pragmatic efficiency and quality improvement. One result of this interest is the UVVM verification platform that is currently being used by around 20% of all FPGA VHDL designers world-wide. He has given many presentations and keynotes on various technical aspects of FPGA development and is running courses on both design and verification of FPGA/ASIC.

|